PXI Mobile Phones & Portable Devices Driver Download For Windows

^ Mobile phones to adopt new, smaller USB connector (PDF) (新聞稿). USB Implementers Forum. 2007-01-04 2007-01-08. ( 原始內容 (PDF) 存檔於2007-01-08). Sony Ericsson PXi For Lefties by yogesh. Hold your horses the PXi is a concept phone designed by a leftie Bence Bogar for lefties the phone is clad in magnesium and comes with huge 3.3 inch touchscreen. The screen rotates automatically like the iPhone and and is optimized for both finger and stylus input. Alcatel Pixi 3 (4.5) Android smartphone. Announced Jan 2015. Features 4.5″ display, MT6572M chipset, 5 MP or 8 MP primary camera, 1780 mAh battery, 4 GB storage, 1000 MB RAM. PXI Express, PXIe PXI Express, PXIe, defined in PXI-5 & PXI-6, enables far higher speeds and increased performance to be accommodated while still providing backward compatibility with older PXI modules. NOKIA Mobile Phones, Inc. 0 Kudos Message 1 of 4 (3,743 Views). Go into the Windows device manager and delete your PCI/PXI device.

- Pxi Mobile Phones & Portable Devices Driver Download For Windows 10

- Pxi Mobile Phones & Portable Devices Driver Download For Windows 8

PXI tutorial includes:

What is PXI?PXI standardPXI chassisPXI bus and backplanePXI controllerPXI cards & modulesPXI softwarePXI ExpressPXImc MultiComputingSet-up & build PXI system

The PXI standard has become widely used in the years since 1998 when it was launched.

PXI has found many applications in fields varying from automatic test to data acquisition. In these fields it has become a very cost efficient and technically effective solution.

One of the key elements in this widespread level of acceptance has been the fact that PXI uses the PCI standard in the communication backplane.

With computers as well as the data acquisition and test automatic applications requiring greater levels of data transfer, higher speeds and additional facilities, PXI has evolved to PXI Express, mirroring the change from PCI to PCI Express.

To achieve the improvements, the PXISA, the organisation that manages the PXI standards released the PXI Express standard that is defined in the PXI-5 (hardware) and PXI-6 (software) specifications.

PXI Express, PXIe advantages

PXI Express offers many advantages over the original PXI system. As a result, most PXI products sold these days are PXI Express enabled.

PXI Express introduces many advantages:

- Increased data bandwidth: By using PCI Express, PXIe backplane technology, PXI Express increases the available PXI bandwidth from 132 MB/s to 8 GB/s. for a more than 60X improvement in bandwidth while still maintaining software and hardware compatibility with PXI modules

- Compatibility: Both software and hardware compatibility is maintained with PXI modules. This allows legacy modules to be used (within their capability) and enables a progressive migration from PXI to PXI Express

- Synchronisation: PXI Express, PXIe provides significantly improved synchronisation capabilities over PXI, enabling it to provide far greater levels of accuracy in certain measurements.

PXI Express development

The development of PXI Express, PXIe was fuelled by the development of the PCI Express specification. This was first released in 2002 and it took until 2004 until PCI Express slots started to appear in mainstream PCs. Many companies including Intel, Dell, Microsoft and HP started to drive the technology.

PXI had established itself well in the industry for applications including from test, control and data acquisition. PXI technology had established itself to the extent that even during downturns in the industry as a whole, the PXI adoption continued to gain momentum against the industry trend. In 2004 PXI achieved a growth of over 40%.

Work started on PXI Express in May 2005 when the PXI Systems Alliance (PXISA) began work on the PXI Express specification. They worked with the PCI Industrial Manufacturers Group (PICMG) to ensure the PCI Express technology was correctly integrated into the PXI Express backplane while still preserving compatibility with the large installed base of PXI existing systems. They had a deadline for completion of late 2005 for the completion of the first release of the document.

PXI Express PXIe basics

PXI Express, PXIe technology takes advantage of the improvements that were introduced in the PCI Express platform.

One of the most notable changes and improvements is the introduction of its point-to-point bus topology. The shared bus used within PCI has been replaced by a shared switch that provides that provides each device with direct access to the bus.

Under the old system, the bus bandwidth was divided between all the devices on the bus, but now each devices has its own data pipeline, thereby considerably increasing the data rate achievable.

Data is sent serially over the bus in packets. This is done through pairs of transmit and receive signals called lanes. These lanes enable 250 MB/s bandwidth per direction, per lane.

Multiple lanes can be grouped together in a variety of different formats: x1, x2, x4, x8, x12, x16, and x32 lane widths thereby increasing the bandwidth to the slot. This increase in data bandwidth enables the need for on-board memory to be minimised while still providing for much faster data streaming.

In order to preserve the backward compatibility with PXI modules, PXI Express specifies PXI Express hybrid slots to deliver signals for both the PCI and PCI Express formats.

PCI Express electrical lines connect the system slot controller to the hybrid slots of the backplane, and as a result PXI Express is able to provide a high-bandwidth path from the controller to backplane slots. To achieve this it uses an inexpensive PCI Express-to-PCI bridge, so that PXI Express is able to provide PCI signalling to all PXI and PXI Express slots to ensure compatibility with PXI modules on the backplane.

Timing and synchronisation

Apart from the increase in speed, one of the key advances in PXIe is the introduction of a far superior timing and synchronisation scheme. With speeds of circuitry increasing, the need arose for far better forms of synchronisation and timing to enable tests requiring tight synchronisation or timing to be performance.

In achieving this, PXI Express, PXIe retains the original timing and synchronization features of PXI for backwards compatibility. It also adds new capabilities.

The key to these is the use of the existing differential connectors and implementing a differential clock system that provides lower latency as well as greater noise immunity and higher speeds.

As a result, PXI Express provides the additional timing and synchronization features of a differential system clock, differential signalling, and differential star triggers.

PXI Express, PXIe is able to provide significant benefits, while still retaining compatibility with older PXI modules. As a result, PXI Express is now standard throughout the industry enabling its performance to be utilised in virtually every application.

More Test Topics:

Data network analyzerDigital MultimeterFrequency counterOscilloscopeSignal generatorsSpectrum analyzerLCR meterDip meter, GDOLogic analyzerRF power meterRF signal generatorLogic probePAT testing & testersTime domain reflectometerVector network analyzerPXIGPIB Boundary scan / JTAG

Return to Test menu . . .

From its inception, PXI has made an impact on the electronics industry by reducing cycle time, development time, size, and cost.

Pxi Mobile Phones & Portable Devices Driver Download For Windows 10

Now there is Revision 2.0 of the PXI Specification, approved by the PXI Systems Alliance only a few months ago, which provides these same benefits for larger, more sophisticated ATE.

Revision 2.0 defines the implementation of multiple PCI bus segments and the routing of synchronization and timing signals across multiple bus segments. It also addresses the needs of high-slot-count ATE and opens the door for more applications that can be accommodated with PXI.

Multiple PCI Bus Segments

The Peripheral Component Interface (PCI) bus is the de facto standard bus used in virtually every desktop computer throughout the world as well as on the PXI backplane. The PCI bus has a multitude of strengths, including processor independence, high data rates, software and operating-system support, peripheral vendor support, and built-in features for future enhancements.

However, the PCI bus is limited to eight loads. In desktop computers, the eight-load limit allows for only three or four peripheral slots because both the card-edge connector and the plug-in peripheral count as loads. Because PXI uses high-performance connectors that do not count as loads, you can get seven peripheral slots.

More peripheral slots can be added through the use of bridges. Desktop computers, industrial computers, and PXI all leverage PCI-to-PCI bridges. The PCI-to-PCI bridge replicates the PCI bus to create an additional PCI bus segment. Each PCI segment is limited to eight loads, with the bridge counting as one. Consequently, a PCI-to-PCI bridge provides desktop and industrial PCs with an additional three slots and PXI with an additional seven.

However, PCI-to-PCI bridges come with trade-offs. While they perform well, more than three bridges on one PCI bus can greatly degrade the performance of the bus. When building high-slot-count, high-performance ATE, this performance drop can greatly increase cycle time and even prevent the use of multiple high-performance instruments in one system. But, because PXI has more peripheral slots per bus segment, it is possible to build high-slot-count systems without sacrificing a high-performance bus.

Synchronization and Timing Signal Routing Across Bus Segments

PCI-to-PCI bridges have been used extensively by the computer industry for several years. PXI uses these same low-cost bridges to replicate the PCI bus across the PXI backplane as found in desktops and industrial PCs.

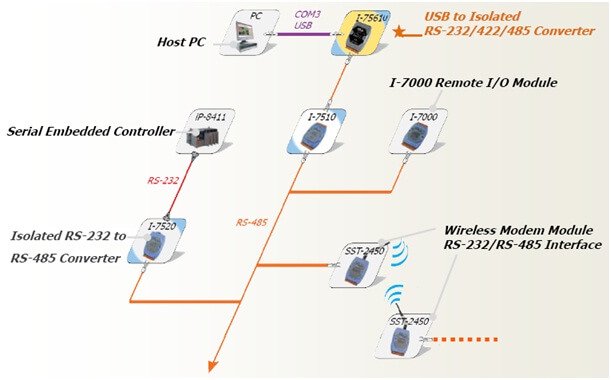

However, PXI also has advanced synchronization and timing signals on the backplane: a dedicated 10-MHz reference clock, a PXI trigger bus, a star trigger bus, and a slot-to-slot local bus (Figure 1). Revision 2.0 of the PXI specification clarifies how to implement these signals across PCI bus segments.

The PXI specification requires that the 10-MHz reference clock be available to every peripheral slot in every bus segment. An independent buffer that is source-impedance matched to the backplane drives the 10-MHz clock to each peripheral slot.

The PXI specification also requires that the PXI trigger lines be bused between segments rather than directly connected. The trigger lines on different bus segments must be logically connected rather than physically connected to maintain signal integrity and allow for incident wave switching of Type A trigger drivers.

Type A trigger drivers are used for clock transmission over the trigger bus and are capable of incident wave switching on rising edges, preventing jitter degradation due to transmission-line effects. Revision 2.0 of the PXI specification allows for the star trigger signals to be routed to peripheral slots beyond the first two bus segments. It also removes the rule that the local bus could not be routed between adjacent slots if adjacent slots were on different bus segments.

Revision 2.0 outlines alternate routings of ID Select (IDSEL) and Interrupt (INT) lines of peripheral slots to accommodate PCI-to-PCI bridges, making alternate local bus routings possible. All of these specifications make designing high-performance, high-slot-count PXI chassis possible.

Do More With High-Slot-Count PXI Systems

High-slot-count PXI systems allow you to do more in a single system because of the advanced synchronization and triggering signals. With high-slot-count systems, you can contain all the instrumentation needed for automated test in one system. So whether you need multiple high-speed digitizers, DMMs, arbitrary waveform generators, switches, or other instruments, you can synchronize your instruments across the PXI backplane to achieve test accuracy and efficiency.

Synchronization and triggering signals increase your system’s accuracy when making time-domain measurements and efficiency when making steady-state measurements. Time-domain measurements characterize the variation of the output of a unit under test (UUT) over time. For these measurements, the accuracy of the measured response not only depends on the accuracy of its magnitude, but also on the time you measure signals.

You can see from Figure 2 that obtaining accurate, repeatable results requires precise triggering. In the steady-state case, the measurement process depends on the time of the measurement. If you measure the signals too early, accuracy suffers because the source output may not have fully settled.

Although you can measure the signals accurately any time after the output has settled, you must minimize the delay to reduce test time. Many test developers insert an arbitrary delay in their test programs to ensure accurate results. While this is a simple fix, test time suffers.

Many test applications call for measurements of several channels simultaneously. For example, with PXI, you can synchronize an arbitrary waveform generator and 10 two-channel high-speed digitizers with a trigger signal that has less than 5 ns of uncertainty.

For steady-state measurements that do not need to be recorded simultaneously, to lower your cost, you will use switches to route the signals to a single DMM. By passing handshaking signals across the PXI backplane between the DMM and the switches, you can optimize the time spent accessing all the nodes. And now with high-slot-count PXI systems, you can perform both of these functions and many others in one test system.

Figure 3 shows an example of a PXI system for automated mobile phone testing. Many measurement functions are combined into one high-slot-count PXI system to perform all test functions required for mobile phones, including keyboard, LCD, RF antenna, speaker-quality, battery, and circuit-board testing.

GenRad Versa Automotive Tester

The GenRad Versa Automotive Tester (GR Versa AT) already leverages multiple PXI bus segments to provide a high-performance test system. It addresses the needs of automotive manufacturers, contract manufacturers, and systems integrators who require a new, compact, tightly integrated test platform.

The GR Versa AT contains three PXI bus segments to deliver a system that houses up to 19 PXI instruments. It includes multiple analog and digital I/O lines, a matrix switching solution, active and passive loads, and multiple communications protocols. With all these devices in one PXI system, the GenRad Versa AT delivers economical, high-speed testing.

Rohde & Schwarz Cellular Phone Tester

The Rohde & Schwarz TS7100 Cellular Phone Tester also leverages multiple PXI bus segments to deliver a high-performance tester for the telecommunications market. It performs parallel testing of several UUTs to obtain maximum speed in highly automated production.

The TS7100 includes digital I/O; a digital multimeter; RS-232 serial, GPIB, general-purpose, and AF switching; and power relay devices. The TS7100 offers a test solution with high throughput and low cost.

Pxi Mobile Phones & Portable Devices Driver Download For Windows 8

Conclusion

PXI already has helped reduce cycle time, development time, size, and cost in ATE. But now with Revision 2.0 of the PXI specification, you can apply all these benefits to high-slot-count ATE. Whether you need to synchronize a large number of PXI instruments, switch a large number of channels, or both, multiple PXI bus segments make it possible without sacrificing performance, test speed, or budget.

About the Author

Brad W. Smith is the PXI product manager at National Instruments and chairman and CEO of the PXI Systems Alliance. He also is an executive-level member of the PCI Industrial Computer Manufacturers Group. Mr. Smith holds a B.S. in mechanical engineering from Texas A&M University. National Instruments, 11500 N. Mopac Expressway, Austin, TX 78759, 800-258-7022, e-mail: brad.w.smith@ni.com.

Return to EE Home Page

Published by EE-Evaluation Engineering

All contents © 2001 Nelson Publishing Inc.

No reprint, distribution, or reuse in any medium is permitted

without the express written consent of the publisher.

June 2001